### **FUJITSU SEMICONDUCTOR**

**CONTROLLER MANUAL**

# F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER MB90560/565 Series HARDWARE MANUAL

# F<sup>2</sup>MC-16LX 16-BIT MICROCONTROLLER MB90560/565 Series HARDWARE MANUAL

### **PREFACE**

### **■** Objectives and Intended Reader

Thank you for purchasing Fujitsu semiconductor products.

The MB90560/565 series was developed as a group of general-purpose models in the F<sup>2</sup>MC-16 LX series, which is a family of original 16-bit single-chip microcontrollers that can be used for application specific IC (ASIC).

This manual is intended for engineers who design products using the MB90560/565 series of microcontrollers. The manual describes the functions and operation of the MB90560/565 series.

### ■ Trademarks

F<sup>2</sup>MC is the abbreviation of FUJITSU Flexible Microcontroller.

Other system and product names mentioned herein are trademarks of their respective owners.

The symbols <sup>™</sup> and ® are sometimes omitted in the text.

### Organization of This Manual

This manual consists of the following 20 chapters:

### **CHAPTER 1 "OVERVIEW"**

This chapter describes the features of the MB90560/565 series.

### **CHAPTER 2 "CPU"**

This chapter describes the functions and operations of the CPU of the MB90560/565 series.

### **CHAPTER 3 "RESETS"**

This chapter describes resets for the MB90560/565 series.

### **CHAPTER 4 "CLOCKS"**

This chapter describes the clocks used by MB90560/565-series.

### CHAPTER 5 "LOW POWER CONSUMPTION MODE"

This chapter describes the low power consumption mode of MB90560/565 series.

### **CHAPTER 6 "INTERRUPTS"**

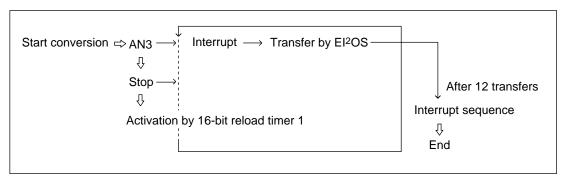

This chapter explains the interrupts and extended intelligent I/O service (EI<sup>2</sup>OS) in the MB905605/565 series.

### **CHAPTER 7 "SETTING A MODE"**

This chapter describes the operating modes of the MB90560/565 series.

### **CHAPTER 8 "I/O PORTS"**

This chapter describes the functions and operations of the I/O ports.

### **CHAPTER 9 "TIMEBASE TIMER"**

This chapter describes the functions and operation of the timebase timer.

### **CHAPTER 10 "WATCHDOG TIMER"**

This chapter describes the functions and operation of the watchdog timer.

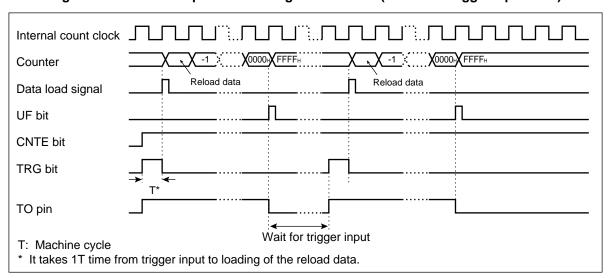

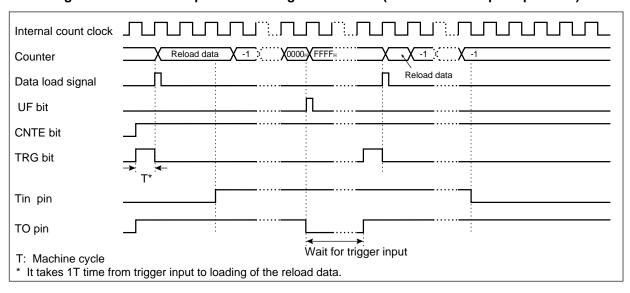

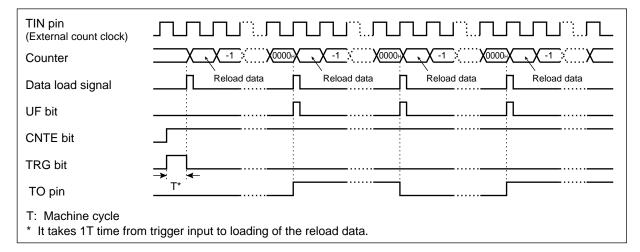

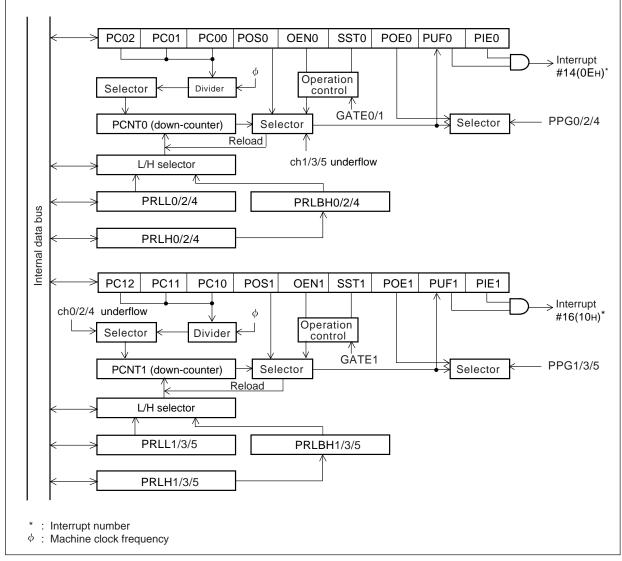

### **CHAPTER 11 "16-BIT RELOAD TIMER"**

The chapter describes the functions and operation of the 16-bit reload timer.

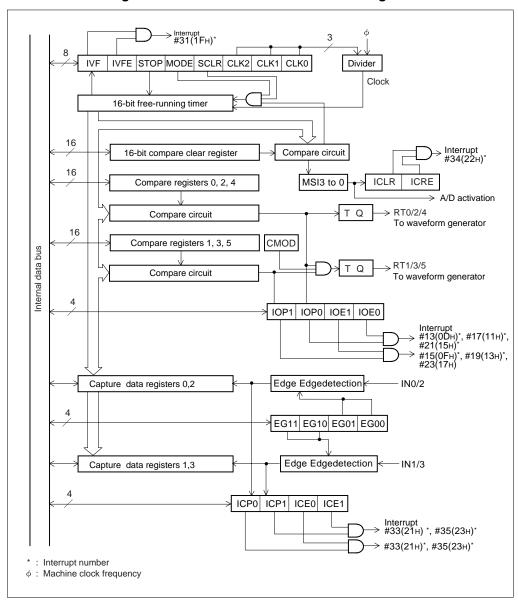

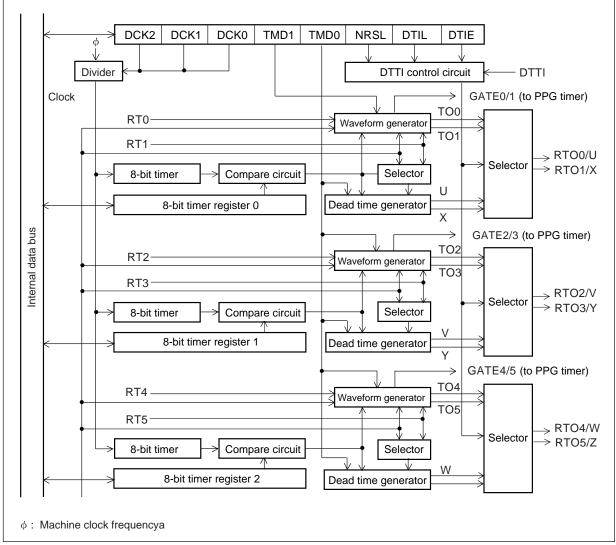

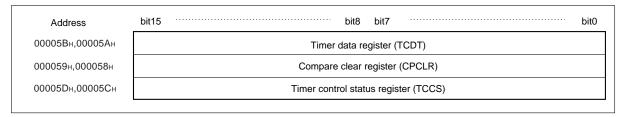

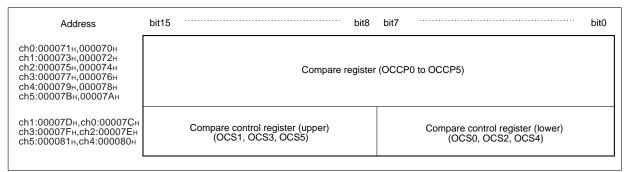

### CHAPTER 12 "MULTIFUNCTIONAL TIMERS"

This chapter describes the operations of the multifunctional timers of MB90560/565 series.

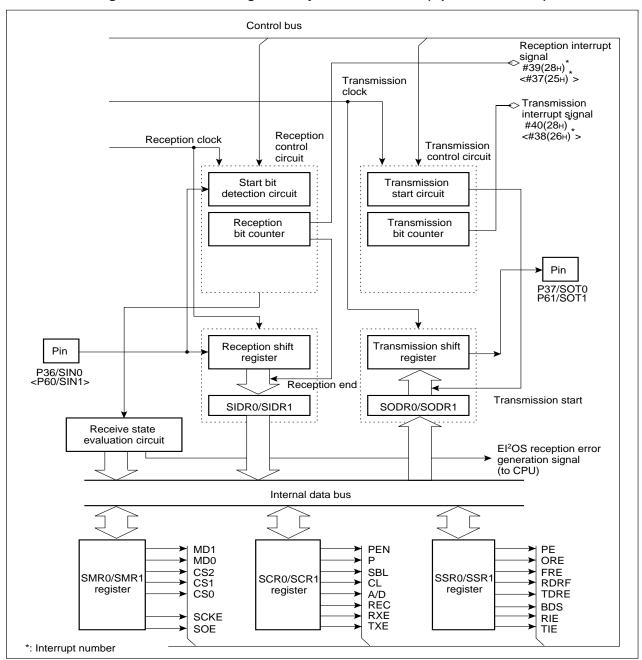

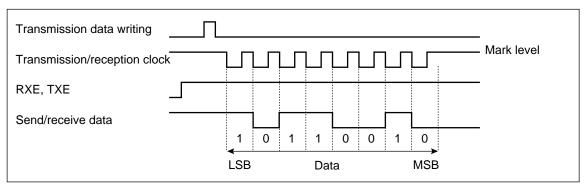

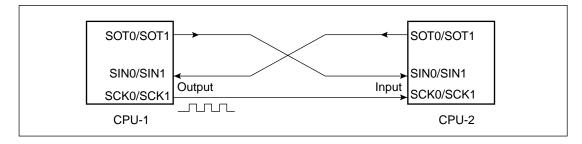

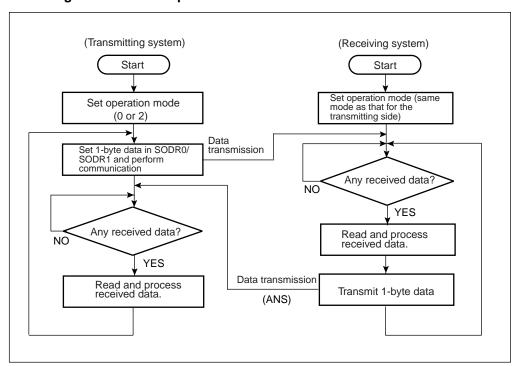

### **CHAPTER 13 "UART"**

This chapter explains the functions and operation of UART.

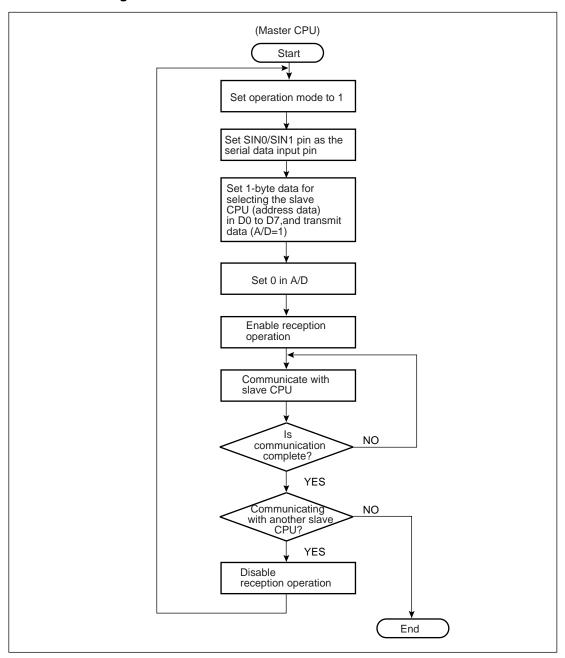

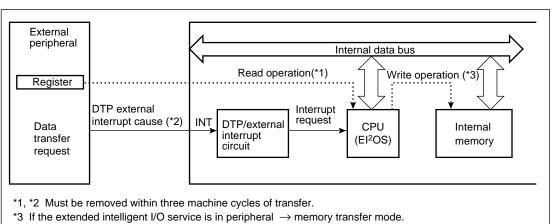

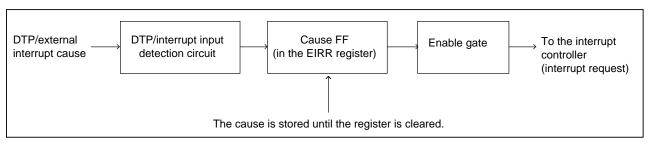

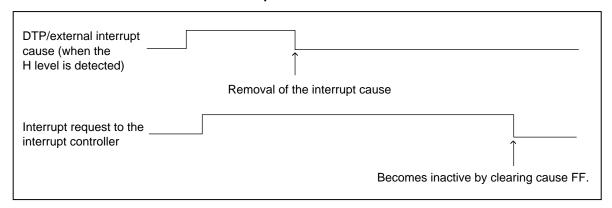

### **CHAPTER 14 "DTP/EXTERNAL INTERRUPT CIRCUIT"**

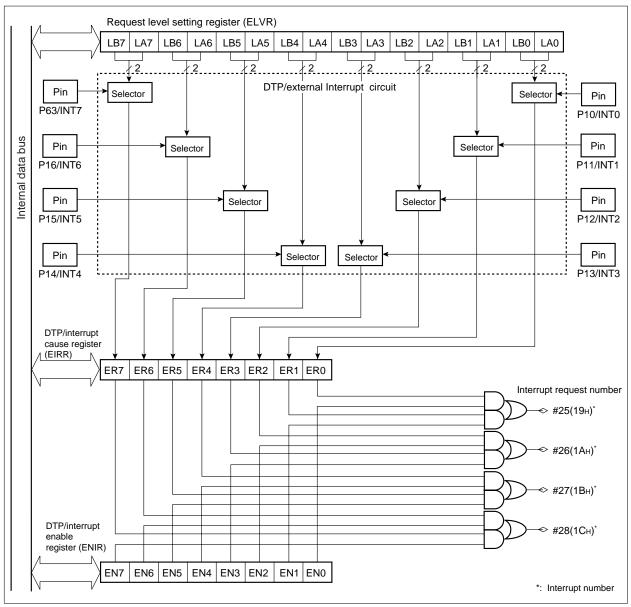

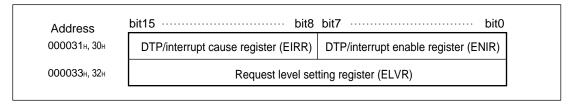

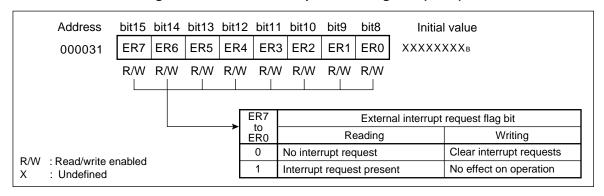

This chapter describes the functions and operation of the DTP/external interrupt circuit.

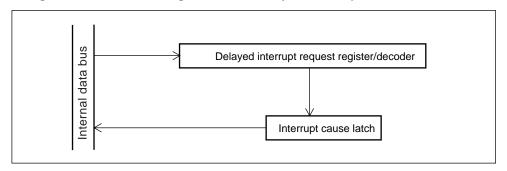

### **CHAPTER 15 "DELAYED INTERRUPT GENERATOR MODULE"**

This chapter describes the functions and operation of the MB90560/565 series delayed interrupt generator module.

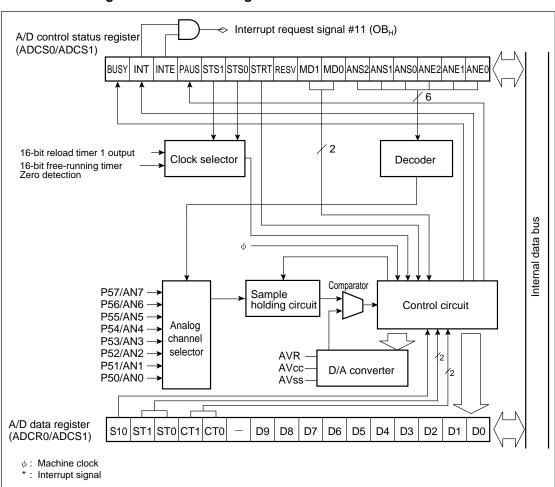

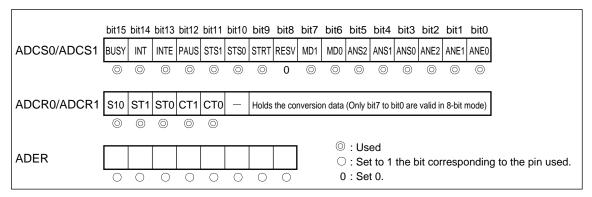

### CHAPTER 16 "8/10-BIT A/D CONVERTER"

This chapter describes the functions and operation of the 8/10-bit A/D converter.

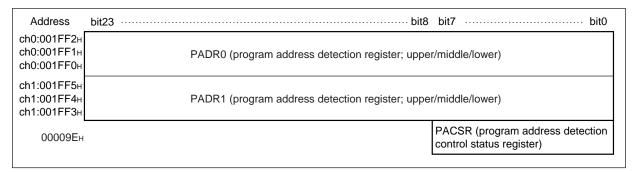

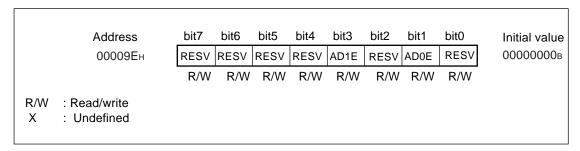

### **CHAPTER 17 "ADDRESS MATCH DETECTION FUNCTION"**

This chapter describes the address match detection function and operation of the MB90560/565 series.

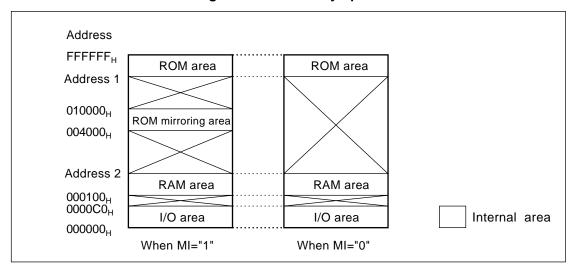

### **CHAPTER 18 "ROM MIRRORING FUNCTION SELECTION MODULE"**

This chapter describes the function and operation of the MB90560/565 series ROM mirroring function selection module.

### **CHAPTER 19 "512K BIT FLASH MEMORY"**

This chapter describes the functions and operations of the 512K-bit (64KB) flash memory of the MB90560/565 series.

### CHAPTER 20 "1M-BIT (128KB) FLASH MEMORY"

This chapter describes the functions and operations of the 1M-bit (128KB) flash memory of the MB90F568.

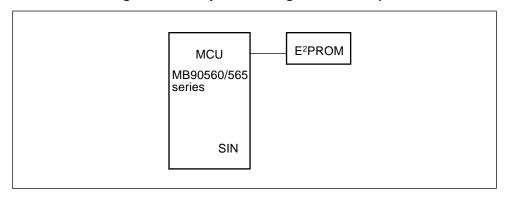

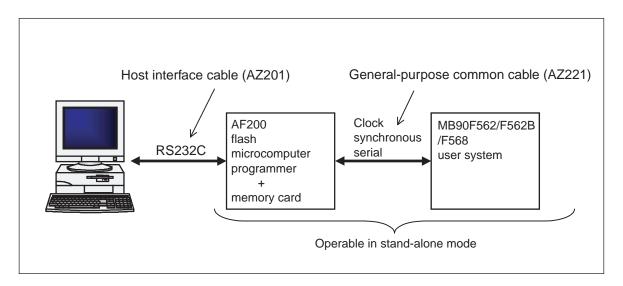

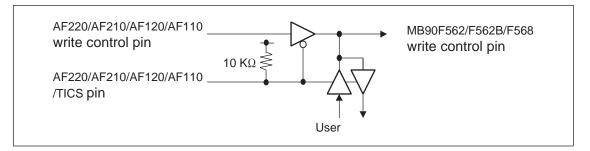

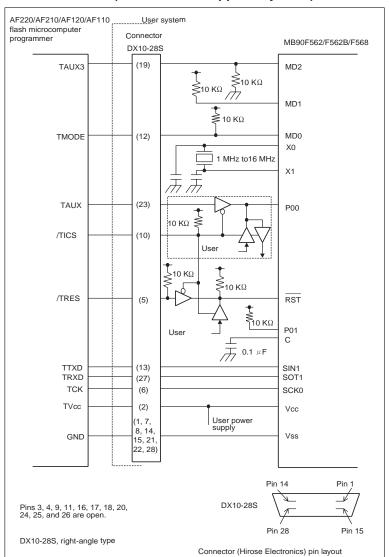

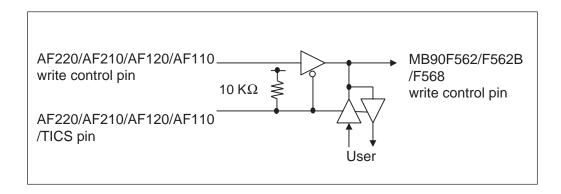

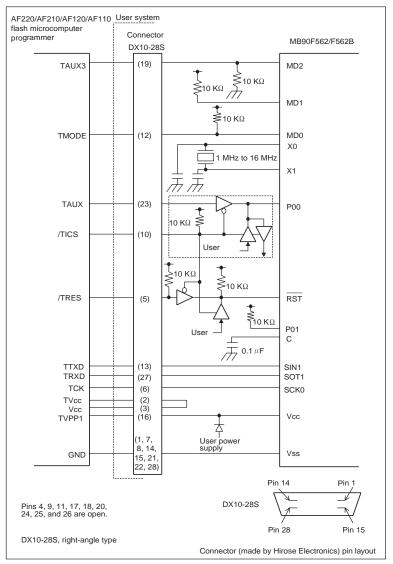

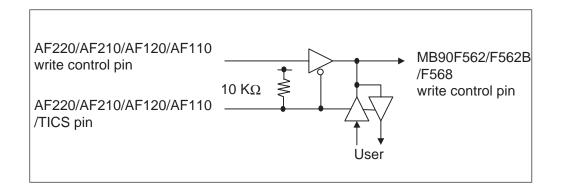

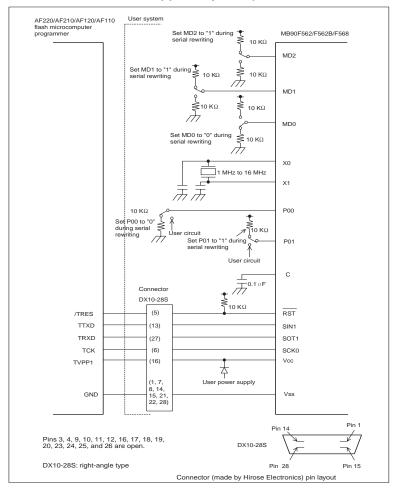

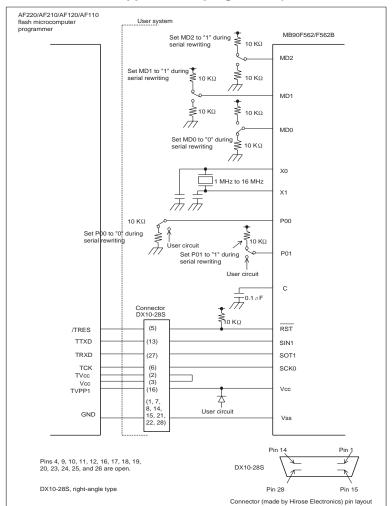

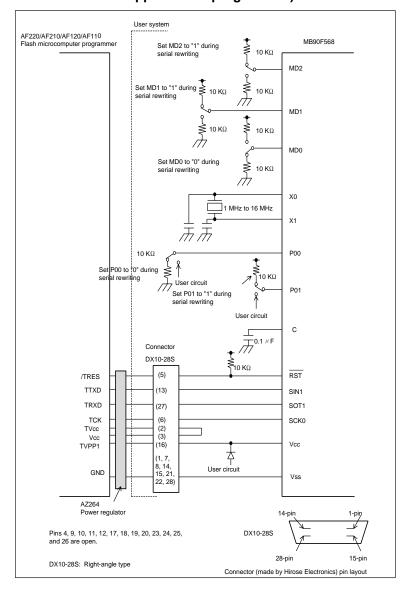

# CHAPTER 21 "EXAMPLE OF MB90F562/F562B/F568 SERIAL PROGRAMMING CONNECTION"

This chapter provides examples of serial programming connection with the AF220/AF210/AF120/AF110 flash microcomputer programmer manufactured by YDC Corporation.

### **APPENDIX**

The appendix provides I/O maps and outlines instructions.

- The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

- The information and circuit diagrams in this document are presented as examples of semiconductor device applications, and are not intended to be incorporated in devices for actual use. Also, FUJITSU is unable to assume responsibility for infringement of any patent rights or other rights of third parties arising from the use of this information or circuit diagrams.

- The products described in this document are designed, and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

- Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

- Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

- If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

# **CONTENTS**

| CHAP | TER 1 OVERVIEW                                                  |    |

|------|-----------------------------------------------------------------|----|

| 1.1  | Features                                                        | 2  |

| 1.2  | Product Lineup                                                  | 5  |

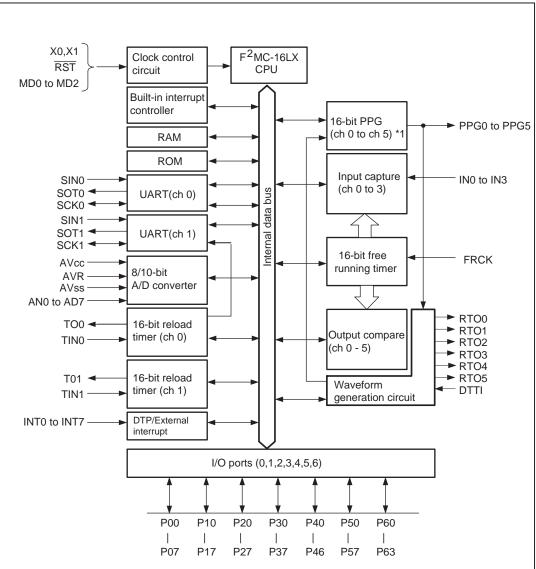

| 1.3  | Block Diagram                                                   | 8  |

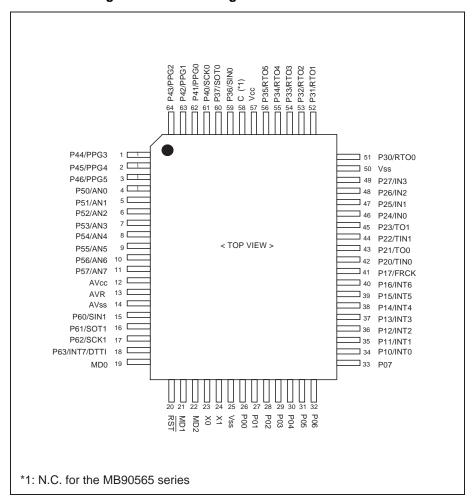

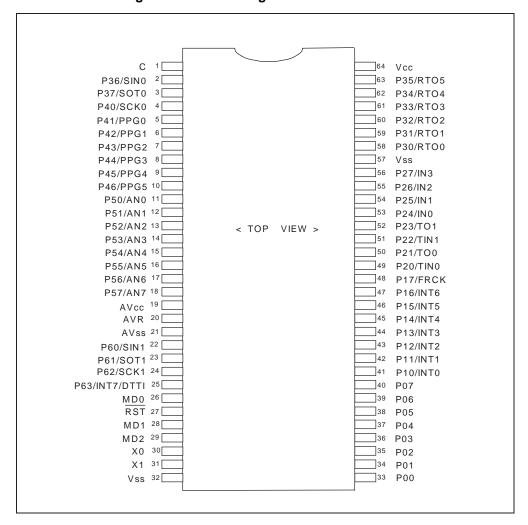

| 1.4  | Pin Assignments                                                 | 9  |

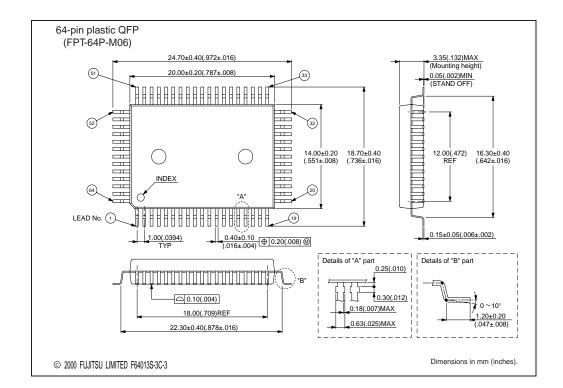

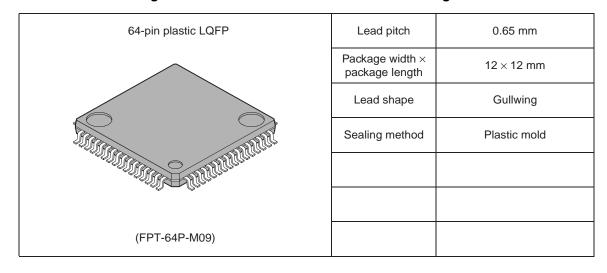

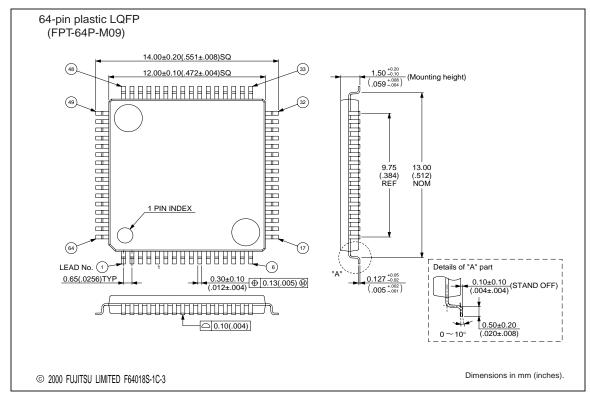

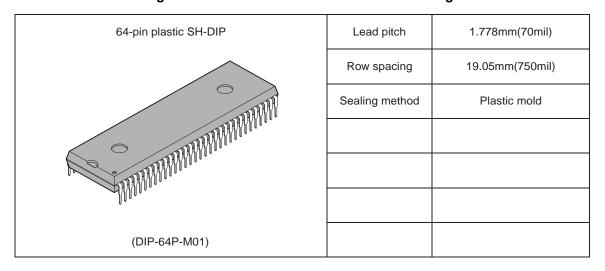

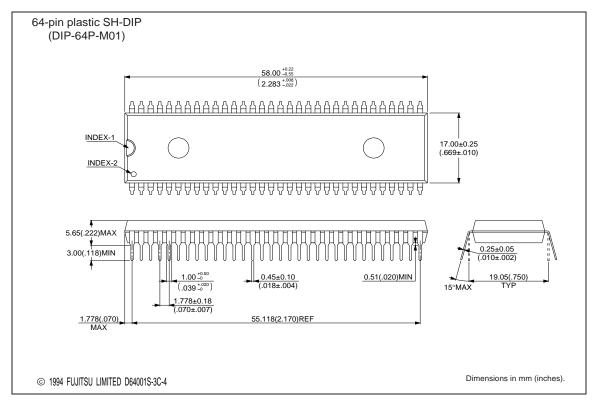

| 1.5  | Package Dimensions                                              | 12 |

| 1.6  | Pin Functions                                                   | 15 |

| 1.7  | I/O Circuit Types                                               | 20 |

| 1.8  | Notes on Handling Devices                                       | 22 |

| СНАР | TER 2 CPU                                                       | 27 |

| 2.1  | CPU                                                             | 28 |

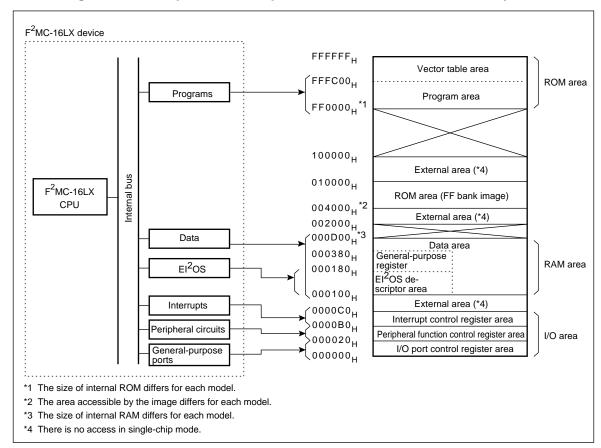

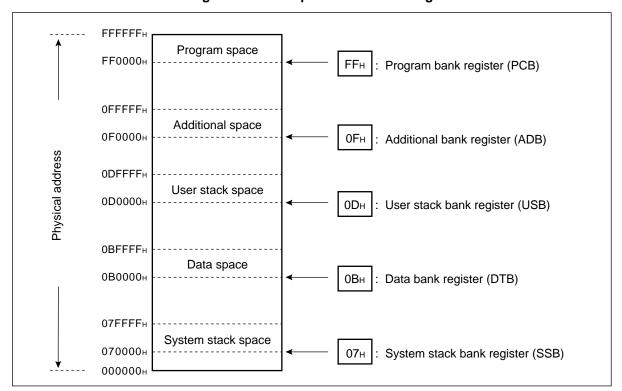

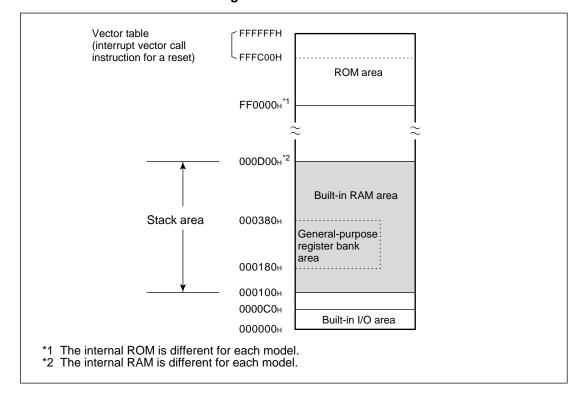

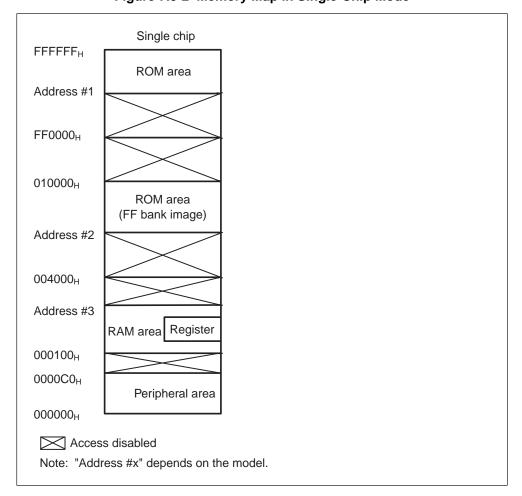

| 2.2  | Memory Space                                                    | 30 |

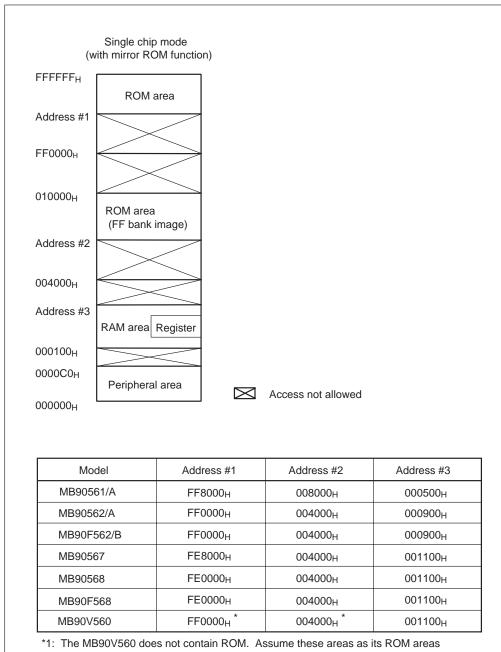

| 2.3  | Memory Maps                                                     | 33 |

| 2.4  | Addressing                                                      | 35 |

| 2.4  | 4.1 Address Specification by Linear Addressing                  | 36 |

| 2.4  | 4.2 Address Specification by Bank Addressing                    | 37 |

| 2.5  | Memory Location of Multibyte Data                               | 39 |

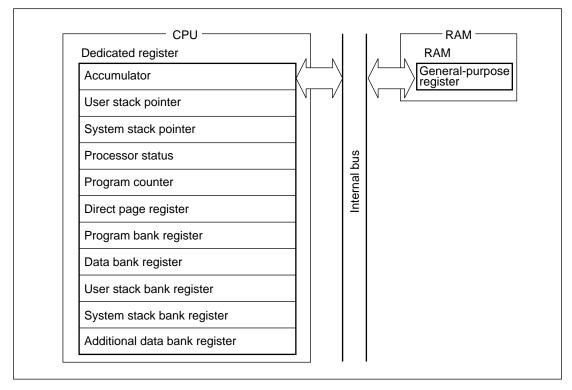

| 2.6  | Registers                                                       | 41 |

| 2.7  | Dedicated Registers                                             | 42 |

| 2.7  | ( )                                                             |    |

| 2.7  | 7.2 Stack Pointers (USP, SSP)                                   | 47 |

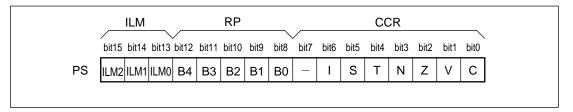

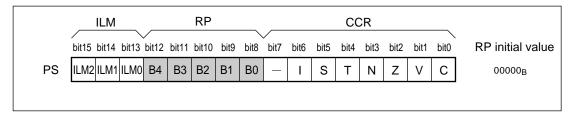

| 2.7  | 7.3 Processor Status (PS)                                       | 49 |

| 2.7  | 7.4 Condition Code Register (PS: CCR)                           | 50 |

| 2.7  | <b>5</b>                                                        |    |

| 2.7  | 7.6 Interrupt Level Mask Register (PS: ILM)                     | 53 |

| 2.7  | 9 ( )                                                           |    |

| 2.7  |                                                                 |    |

| 2.7  |                                                                 |    |

| 2.8  | General-Purpose Registers                                       |    |

| 2.9  | Prefix Codes                                                    |    |

| 2.9  | , , , , ,                                                       |    |

| 2.9  | • ,                                                             |    |

| 2.9  | 3 3 11 ( )                                                      |    |

| 2.9  |                                                                 |    |

| 2.9  | 9.5 Notes on Using the "DIV A, Ri" or "DIVW A, RWi" Instruction | 66 |

| СНАР | TER 3 RESETS                                                    | 69 |

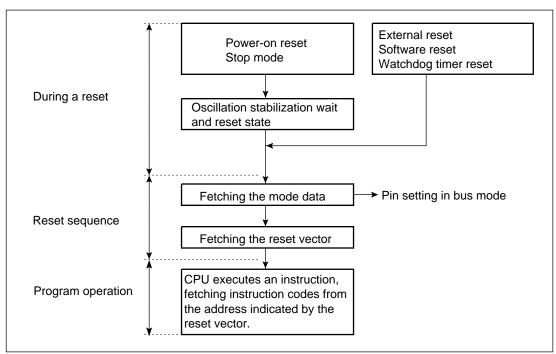

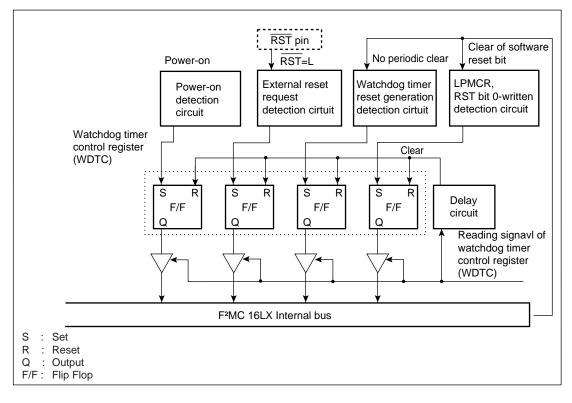

| 3.1  | Resets                                                          | 70 |

| 3.2  | Reset Causes and Oscillation Stabilization Wait Intervals       | 72 |

| 3.3  | External Reset Pin                                              | 74 |

| 3.4  | Reset Operation                                                 | 75 |

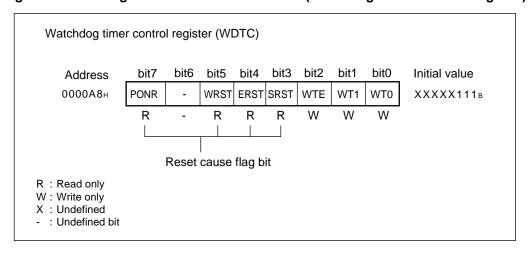

| 3.5  | Reset Cause Bits                                                | 77 |

| 3.6  | Status of Pins in a Reset                                       | 80 |

| <b>CHAP</b> | PTER 4 CLOCKS                                                                               | 81  |

|-------------|---------------------------------------------------------------------------------------------|-----|

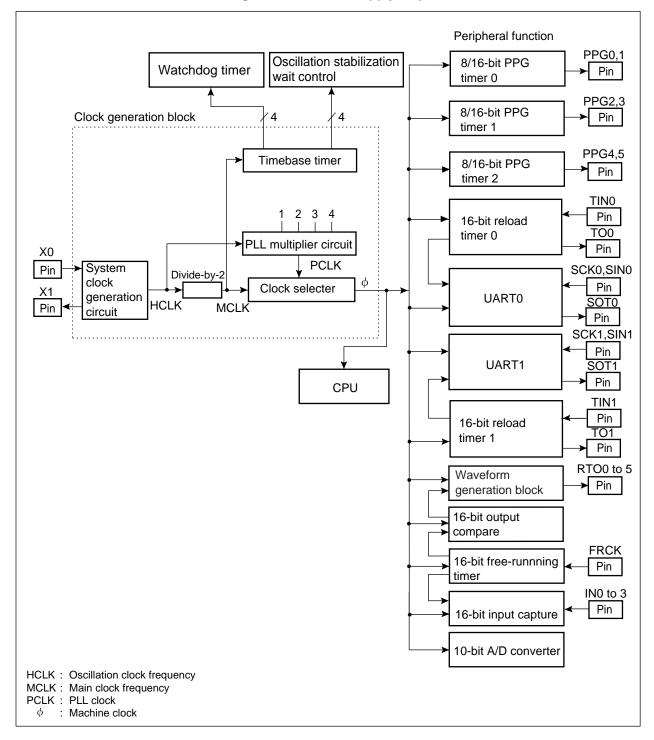

| 4.1         | Clocks                                                                                      | 82  |

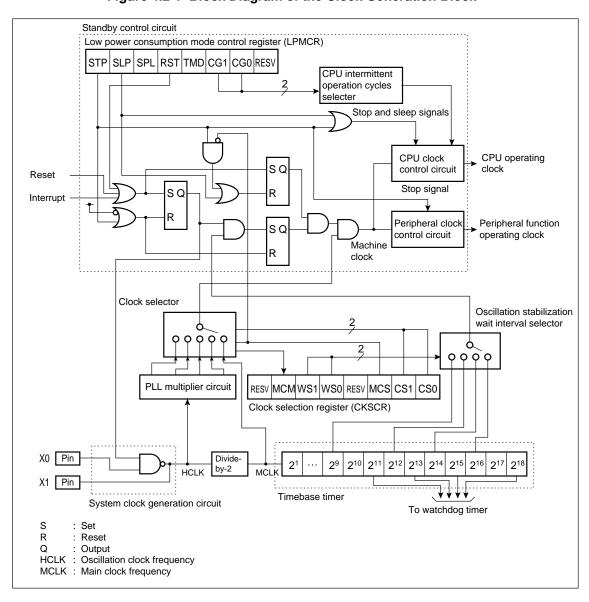

| 4.2         | Block Diagram of the Clock Generation Block                                                 | 84  |

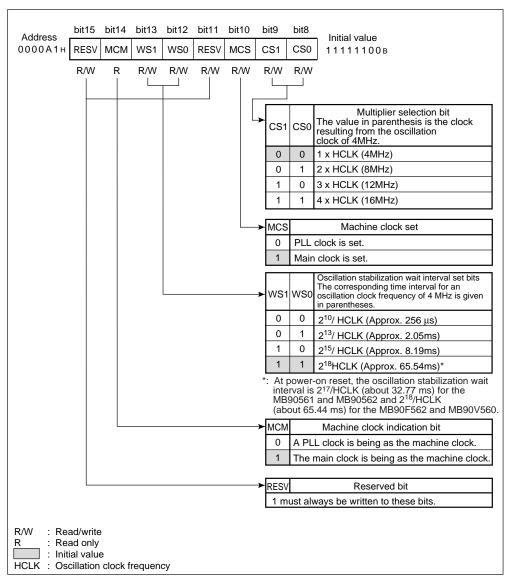

| 4.3         | Clock Selection Register (CKSCR)                                                            | 86  |

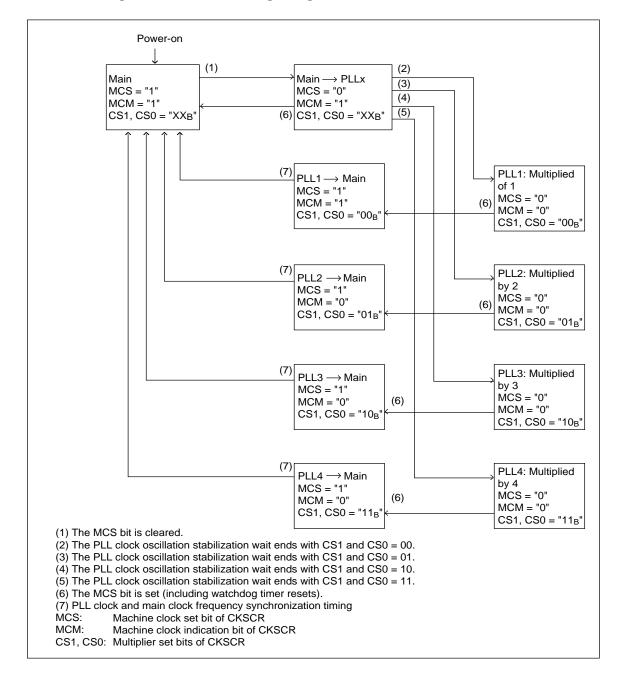

| 4.4         | Clock Mode                                                                                  |     |

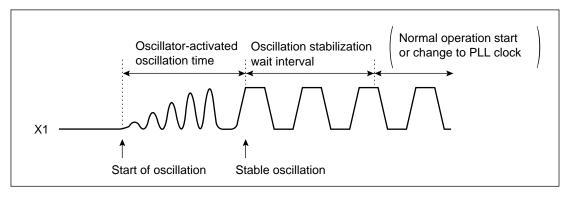

| 4.5         | Oscillation Stabilization Wait Interval                                                     | 90  |

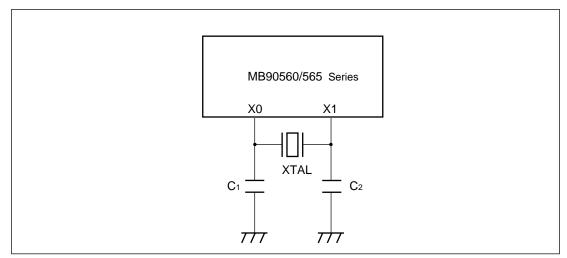

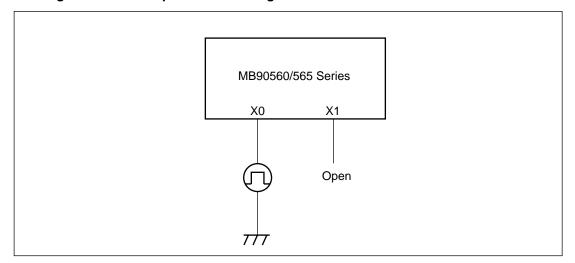

| 4.6         | Connection of an Oscillator or an External Clock to the Microcontroller                     | 91  |

| СНАР        | PTER 5 LOW POWER CONSUMPTION MODE                                                           | 93  |

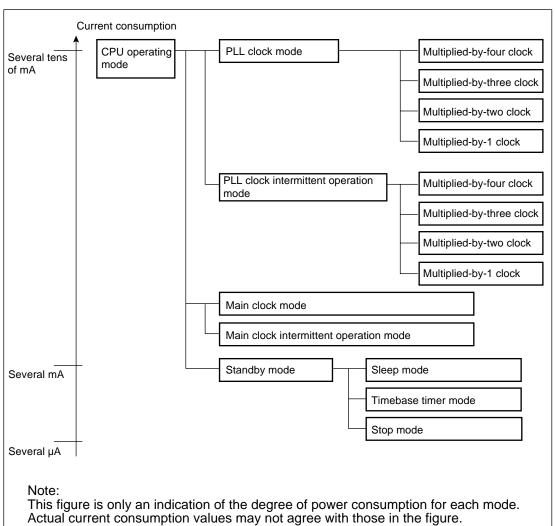

| 5.1         | Low Power Consumption Mode                                                                  | 94  |

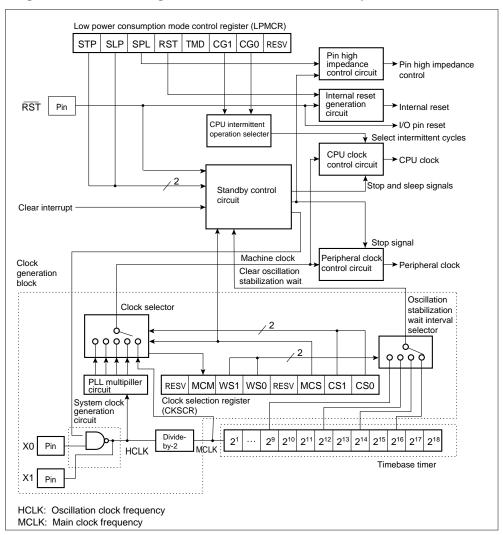

| 5.2         | Block Diagram of the Low Power Consumption Control Circuit                                  |     |

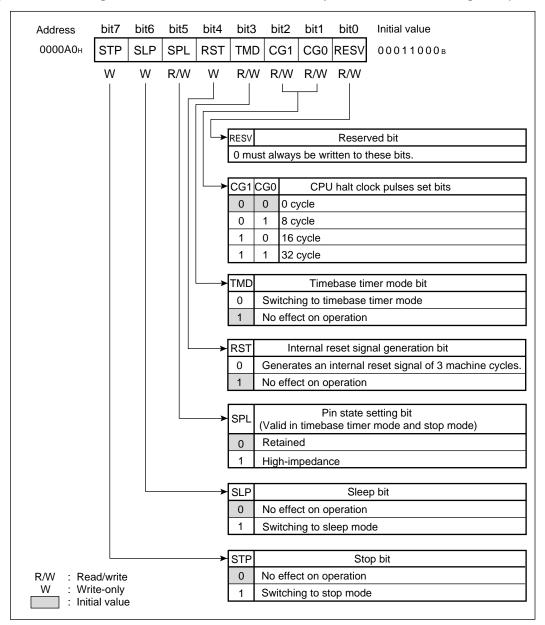

| 5.3         | Low Power Consumption Mode Control Register (LPMCR)                                         |     |

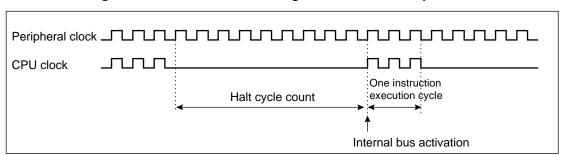

| 5.4         | CPU Intermittent Operation Mode                                                             | 101 |

| 5.5         | Standby Mode                                                                                |     |

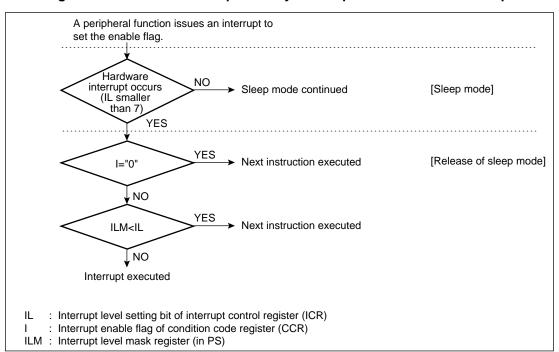

| 5.5         | 5.1 Sleep Mode                                                                              | 103 |

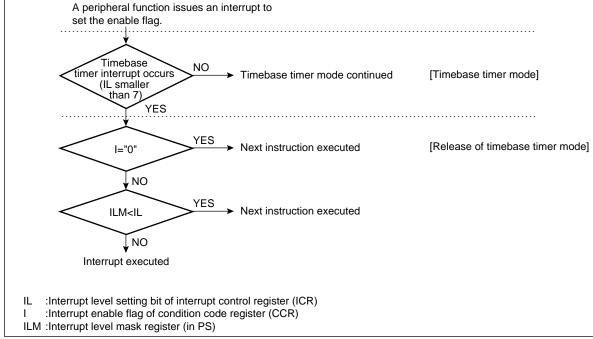

| 5.5         | 5.2 Timebase Timer Mode                                                                     | 105 |

| 5.5         | '                                                                                           |     |

| 5.6         | Status Change Diagram                                                                       |     |

| 5.7         | Status of Pins in Standby Mode and during Hold and Reset                                    |     |

| 5.8         | Usage Notes on Low Power Consumption Mode                                                   | 111 |

| СНАР        | PTER 6 INTERRUPTS                                                                           | 113 |

| 6.1         | Interrupts                                                                                  | 114 |

| 6.2         | Interrupt Causes and Interrupt Vectors                                                      | 116 |

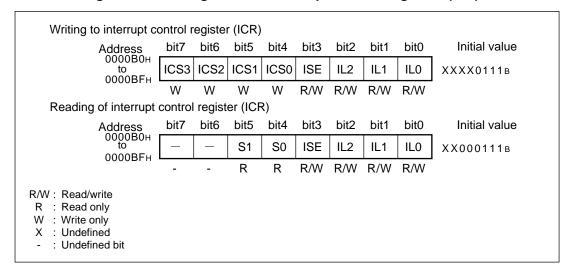

| 6.3         | Interrupt Control Registers (ICR) and Peripheral Functions (Resource)                       |     |

| 6.3         | 7                                                                                           |     |

| 6.3         | 3.2 Interrupt Control Register (ICR) Functions                                              | 124 |

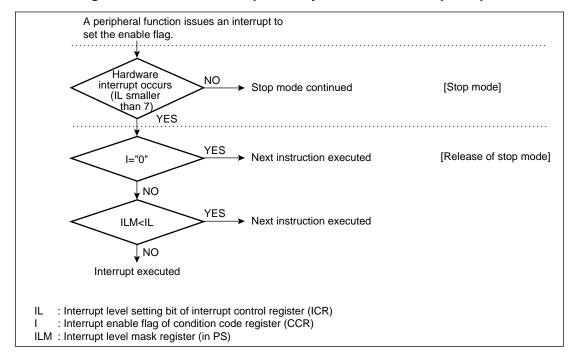

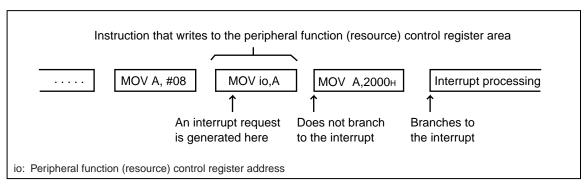

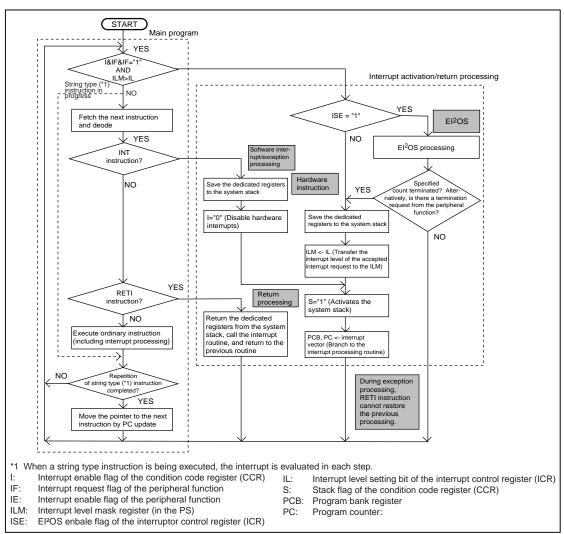

| 6.4         | Hardware Interrupts                                                                         | 127 |

| 6.4         | '                                                                                           |     |

| 6.4         | 4.2 Processing for Interrupt Operation                                                      | 132 |

| 6.4         | 4.3 Procedure for Using Hardware Interrupts                                                 | 133 |

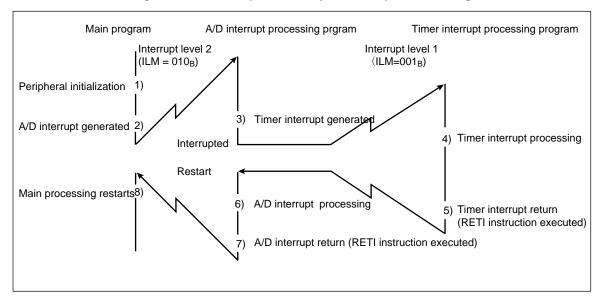

| 6.4         | 4.4 Multiple Interrupts                                                                     |     |

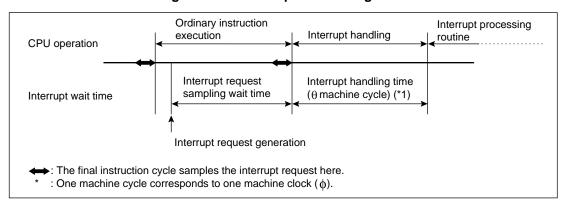

| 6.4         | 4.5 Hardware Interrupt Processing Time                                                      | 137 |

| 6.5         | Software Interrupts                                                                         |     |

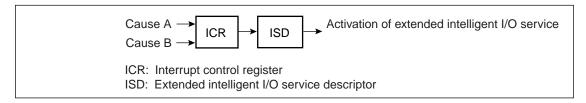

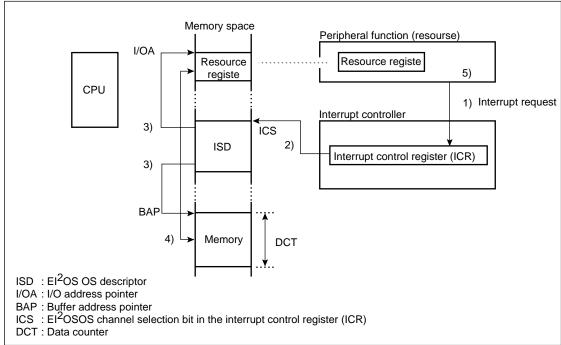

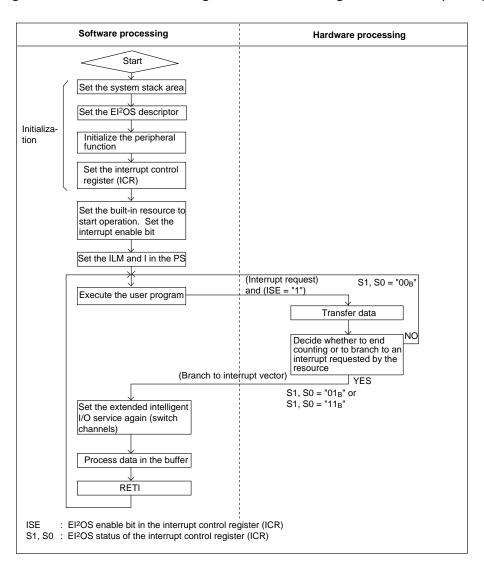

| 6.6         | Interrupt of Extended Intelligent I/O Service (EI <sup>2</sup> OS)                          |     |

| 6.6         | 3                                                                                           |     |

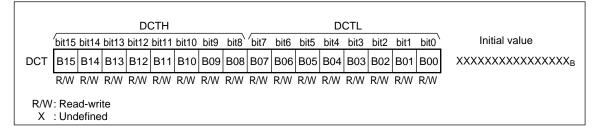

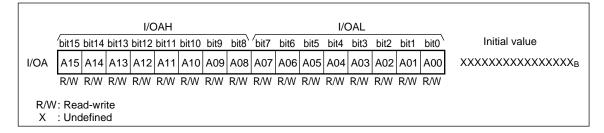

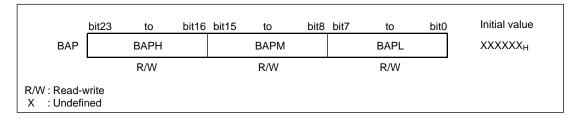

| 6.6         | 6.2 Registers of the Extended Intelligent I/O Service (EI <sup>2</sup> OS) Descriptor (ISD) |     |

| 6.6         | • • • • • • • • • • • • • • • • • • • •                                                     |     |

| 6.6         | 6.4 Procedure for Using the Extended Intelligent I/O Service (EI <sup>2</sup> OS)           |     |

| 6.6         | 6.5 Processing Time of the Extended Intelligent I/O Service (EI <sup>2</sup> OS)            | 150 |

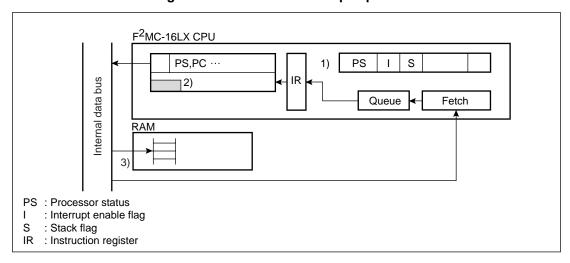

| 6.7         | Exception Processing Interrupt                                                              |     |

| 6.8         | Stack Operations for Interrupt Processing                                                   |     |

| 6.9         | Sample Programs for Interrupt Processing                                                    | 156 |

| СНАР        | PTER 7 SETTING A MODE                                                                       | 159 |

| 7.1         | Setting a Mode                                                                              |     |

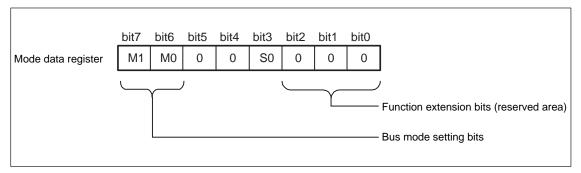

| 7.2         | Mode Pins (MD2 to MD0)                                                                      |     |

| 7.3         | Mode Data Register                                                                          |     |

| 8.1       Overview of I/O Ports       168         8.2       Registers for I/O ports       168         8.3       Port 0       169         8.3.1       Port 0 Registers (PDRO, DDRO, and RDRO)       171         8.3.2       Operation of Port 0       173         8.4       Port 1       175         8.4.1       Port 1 Registers (PDR1, DDR1, and RDR1)       177         8.5       Port 2       183         8.5.1       Port 2 Registers (PDR2 and DDR2)       183         8.5.2       Operation of Port 2       184         8.6.1       Port 3 Registers (PDR3 and DDR3)       188         8.6.1       Port 3 Registers (PDR3 and DDR3)       188         8.6.2       Operation of Port 3       189         8.7       Port 4       191         8.7.1       Port 4 Registers (PDR4 and DDR4)       193         8.7.2       Operation of Port 4       194         8.8       Port 5       206         8.8.1       Port 6 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9       Port 6 Registers (PDR6 and DDR6)       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       204 <th>CHAP</th> <th>TER 8</th> <th> 165</th>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | CHAP  | TER 8                                         | 165 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------|-----|

| 8.3 Port 0 8.3.1 Port 0 Registers (PDR0, DDR0, and RDR0) 8.3.1 Port 0 Registers (PDR0, DDR0, and RDR0) 171 8.4 Port 1 8.4.2 Port 1 Registers (PDR1, DDR1, and RDR1) 175 8.4.1 Port 1 Registers (PDR1, DDR1, and RDR1) 177 8.4.2 Operation of Port 1 179 8.5 Port 2 181 8.5.1 Port 2 Registers (PDR2 and DDR2) 183 8.5.2 Operation of Port 2 184 8.6 Port 3 186 8.6.1 Port 3 Registers (PDR3 and DDR3) 186 8.6.1 Port 3 Registers (PDR3 and DDR3) 187 8.7 Port 4 191 8.7.1 Port 4 Registers (PDR4 and DDR4) 187 8.7 Port 4 191 8.7.1 Port 4 Registers (PDR4 and DDR4) 189 8.7.2 Operation of Port 4 194 8.8 Port 5 196 8.8.1 Port 5 Registers (PDR5, DDR5, and ADER) 188 8.8.2 Operation of Port 5 189 8.8.2 Operation of Port 5 189 8.8.2 Operation of Port 6 189 8.9 Port 6 190 8.9 | 8.1   | Overview of I/O Ports                         | 166 |

| 8.3.1 Port 0 Registers (PDR0, DDR0, and RDR0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 8.2   | Registers for I/O ports                       | 168 |

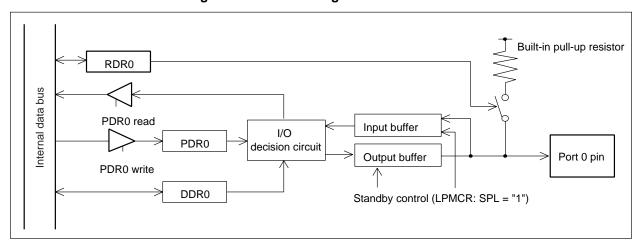

| 8.3.2 Operation of Port 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.3   | Port 0                                        |     |

| 8.4 Port 1       175         8.4.1 Port 1 Registers (PDR1, DDR1, and RDR1)       177         8.4.2 Operation of Port 1       179         8.5 Port 2       181         8.5.1 Port 2 Registers (PDR2 and DDR2)       183         8.5.2 Operation of Port 2       184         8.6. Port 3       186         8.6.1 Port 3 Registers (PDR3 and DDR3)       188         8.6.2 Operation of Port 3       189         8.7 Port 4       193         8.7.1 Port 4 Registers (PDR4 and DDR4)       193         8.7.2 Operation of Port 4       194         8.8 Port 5       196         8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 6       200         8.9.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       221                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 8.3   | .1 Port 0 Registers (PDR0, DDR0, and RDR0)    | 171 |

| 8.4.1       Port 1 Registers (PDR1, DDR1, and RDR1)       177         8.4.2       Operation of Port 1       179         8.5       Port 2       181         8.5.1       Port 2 Registers (PDR2 and DDR2)       183         8.5.2       Operation of Port 2       184         8.6       Port 3       188         8.6.1       Port 3 Registers (PDR3 and DDR3)       188         8.6.2       Operation of Port 3       189         8.7       Port 4       193         8.7.2       Operation of Port 4       193         8.8.1       Port 5 Registers (PDR4 and DDR4)       193         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       206         8.9.1       Port 6 Registers (PDR6 and DDR6)       202         8.9.2       Operation of Port 6       205         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       214         9.4       Timebase Timer C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 8.3   | .2 Operation of Port 0                        | 173 |

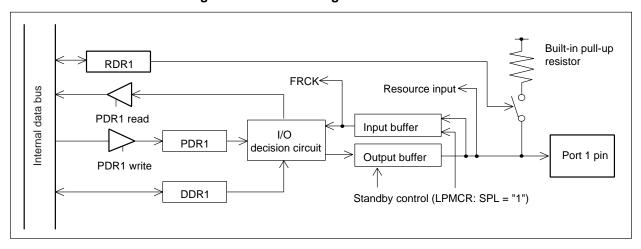

| 8.4.2 Operation of Port 1       179         8.5 Port 2       181         8.5.1 Port 2 Registers (PDR2 and DDR2)       183         8.5.2 Operation of Port 2       184         8.6 Port 3       186         8.6.1 Port 3 Registers (PDR3 and DDR3)       188         8.6.2 Operation of Port 3       189         8.7 Port 4       191         8.7.1 Port 4 Registers (PDR4 and DDR4)       193         8.7.2 Operation of Port 4       194         8.8 Port 5       196         8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 5       200         8.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 16       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       216         9.7 Sample Program for the Watchdog Timer       222         10.1 Overview of the Watchdog Timer       224                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.4   | Port 1                                        | 175 |

| 8.5       Port 2       181         8.5.1       Port 2 Registers (PDR2 and DDR2)       183         8.5.2       Operation of Port 3       186         8.6.1       Port 3 Registers (PDR3 and DDR3)       188         8.6.2       Operation of Port 3       189         8.7       Port 4       191         8.7.1       Port 4 Registers (PDR4 and DDR4)       193         8.7.2       Operation of Port 4       194         8.8       Port 5       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9       Port 6       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Port 6       205         8.10       Sample I/O Port Program       207         CHAPTER 9       TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Stimer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer Program <t< td=""><td>8.4</td><td>.1 Port 1 Registers (PDR1, DDR1, and RDR1)</td><td> 177</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.4   | .1 Port 1 Registers (PDR1, DDR1, and RDR1)    | 177 |

| 8.5.1       Port 2 Registers (PDR2 and DDR2)       183         8.5.2       Operation of Port 2       184         8.6       Port 3       186         8.6.1       Port 3 Registers (PDR3 and DDR3)       188         8.6.2       Operation of Port 3       188         8.7       Port 4       191         8.7.1       Port 4 Registers (PDR4 and DDR4)       193         8.7.2       Operation of Port 4       194         8.8       Port 5       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9       Port 6       Registers (PDR6 and DDR6)       204         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Interrupts       214         9.4       Timebase Timer Interrupts       214         9.6       Usage Notes on the Timebase Timer       227         9.7       Sample Program for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 8.4   | .2 Operation of Port 1                        | 179 |

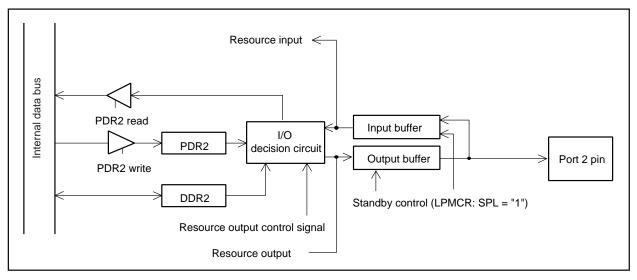

| 8.5.2 Operation of Port 2       184         8.6 Port 3       186         8.6.1 Port 3 Registers (PDR3 and DDR3)       188         8.6.2 Operation of Port 3       189         8.7 Port 4       191         8.7.1 Port 4 Registers (PDR4 and DDR4)       193         8.7.2 Operation of Port 4       194         8.8 Port 5       196         8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 5       200         8.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       220         9.7 Sample Program for the Timebase Timer Program       221         10.1 Overview of the Watchdog Timer       222         10.3 Watchdog Timer Control Register (WDTC)       227                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.5   | Port 2                                        | 181 |

| 8.6. Port 3       186         8.6.1 Port 3 Registers (PDR3 and DDR3)       188         8.6.2 Operation of Port 3       189         8.7 Port 4       191         8.7.1 Port 4 Registers (PDR4 and DDR4)       193         8.7.2 Operation of Port 4       194         8.8 Port 5       196         8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 5       200         8.9.1 Port 6 Registers (PDR6 and DDR6)       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       220         9.7 Sample Program for the Timebase Timer       220         9.7 Sample Program for the Watchdog Timer       224         10.1 Overview of the Watchdog Timer       225         10.2 Configuration of the Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.5   | .1 Port 2 Registers (PDR2 and DDR2)           | 183 |

| 8.6.1       Port 3 Registers (PDR3 and DDR3)       188         8.6.2       Operation of Port 3       189         8.7       Port 4       191         8.7.1       Port 4 Registers (PDR4 and DDR4)       193         8.7.2       Operation of Port 4       194         8.8       Port 5       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9       Port 6       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Port 6       205         8.10       Sample I/O Port Program       207         CHAPTER 9       TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer Program       220         9.7       Sample Program for the Vatchdog Timer       224         10.2       Configura                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.5   | .2 Operation of Port 2                        | 184 |

| 8.6.2 Operation of Port 3       189         8.7 Port 4       191         8.7.1 Port 4 Registers (PDR4 and DDR4)       193         8.7.2 Operation of Port 4       194         8.8 Port 5       196         8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 5       200         8.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer Program       221         10.1 Overview of the Watchdog Timer       222         10.2 Configuration of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 8.6   | Port 3                                        | 186 |

| 8.7       Port 4 Registers (PDR4 and DDR4)       193         8.7.2       Operation of Port 4       194         8.8       Port 5       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9.1       Port 6 Registers (PDR6 and DDR6)       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       205         8.10       Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.2       Configuration of the Timebase Timer       212         9.5       Operation of the Timebase Timer       214         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer Program       221         9.7       Sample Program for the Timebase Timer Program       221         10.1       Overview of the Watchdog Timer       222         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.6   | .1 Port 3 Registers (PDR3 and DDR3)           | 188 |

| 8.7.1       Port 4 Registers (PDR4 and DDR4)       193         8.7.2       Operation of Port 4       194         8.8       Port 5       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9       Port 6       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Port 6       205         8.10       Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer Program       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.6   | .2 Operation of Port 3                        | 189 |

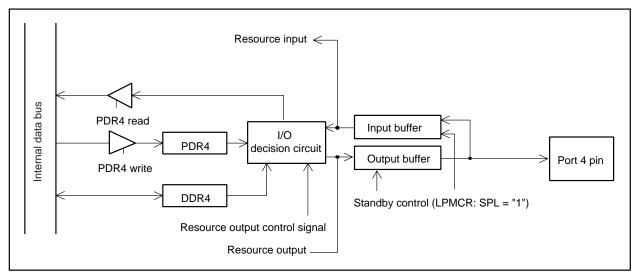

| 8.7.2 Operation of Port 4       194         8.8 Port 5       196         8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 5       200         8.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer Program       221         9.7 Sample Program for the Timebase Timer Program       221         10.1 Overview of the Watchdog Timer       224         10.2 Configuration of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.7   | Port 4                                        | 191 |

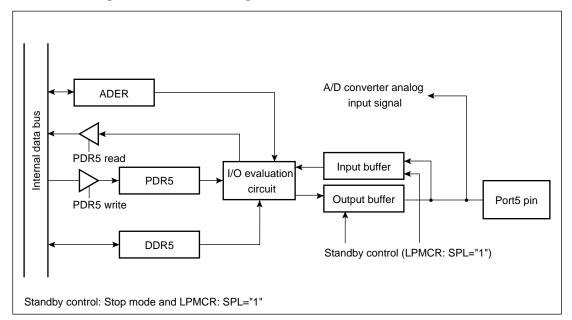

| 8.8       Port 5       196         8.8.1       Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2       Operation of Port 5       200         8.9       Port 6       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Port 6       205         8.10       Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer       221         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       233         10.5       Usage Notes on the Watchdog Timer       233                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 8.7   | .1 Port 4 Registers (PDR4 and DDR4)           | 193 |

| 8.8.1 Port 5 Registers (PDR5, DDR5, and ADER)       198         8.8.2 Operation of Port 5       200         8.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       220         9.7 Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1 Overview of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         10.6 Sample Program for the Watchdog Timer       232         10.6 Sample Program for the Watchdog Timer       232         11.1 Overview of the 16-Bit Reload Timer       233         11.2 Configuration of the 16-Bit Reloa                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 8.7   | .2 Operation of Port 4                        | 194 |

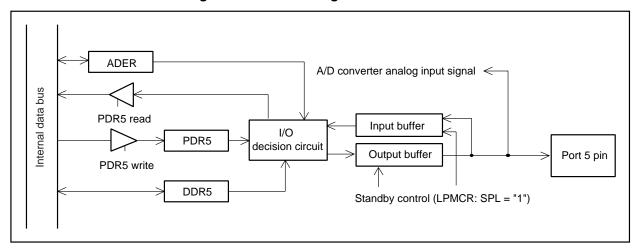

| 8.8.2 Operation of Port 5       200         8.9 Port 6       202         8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer Program       220         9.7 Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1 Overview of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       229         10.5 Usage Notes on the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1 Overview of the 16-Bit Reload Timer       234         11.2 Configuration of the 16-Bit Reload Timer       237         11.3 16-Bit Reload Timer Pins       239 <td>8.8</td> <td>Port 5</td> <td> 196</td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 8.8   | Port 5                                        | 196 |

| 8.9       Port 6       202         8.9.1       Port 6 Registers (PDR6 and DDR6)       204         8.9.2       Operation of Port 6       205         8.10       Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer Program       220         9.7       Sample Program for the Timebase Timer Program       221         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         10.5       Usage Notes on the Watchdog Timer       232         10.6       Sample Program for the Watchdog Timer       232         10.6       Sample Progra                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 8.8   | .1 Port 5 Registers (PDR5, DDR5, and ADER)    | 198 |

| 8.9.1 Port 6 Registers (PDR6 and DDR6)       204         8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer Program       220         9.7 Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1 Overview of the Watchdog Timer       224         10.2 Configuration of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       229         10.5 Usage Notes on the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1 Overview of the 16-Bit Reload Timer       234         11.2 Configuration of the 16-Bit Reload Timer       234         11.2 Configuration of the 16-Bit Reload Timer       237                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.8   | .2 Operation of Port 5                        | 200 |

| 8.9.2 Operation of Port 6       205         8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer Program       220         9.7 Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1 Overview of the Watchdog Timer       224         10.2 Configuration of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       229         10.5 Usage Notes on the Watchdog Timer       229         10.5 Usage Notes on the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1 Overview of the 16-Bit Reload Timer       234         11.2 Configuration of the 16-Bit Reload Timer       237         11.3 16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8.9   | Port 6                                        | 202 |

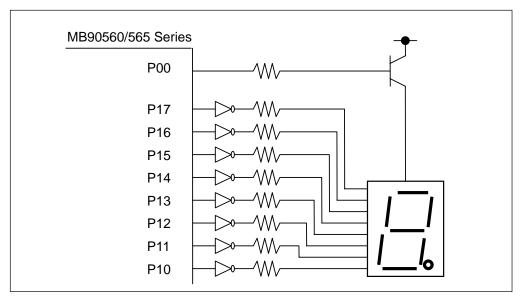

| 8.10 Sample I/O Port Program       207         CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer Program       220         9.7 Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1 Overview of the Watchdog Timer       224         10.2 Configuration of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       229         10.5 Usage Notes on the Watchdog Timer       229         10.5 Sample Program for the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1 Overview of the 16-Bit Reload Timer       234         11.2 Configuration of the 16-Bit Reload Timer       237         11.3 16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 8.9   | .1 Port 6 Registers (PDR6 and DDR6)           | 204 |

| CHAPTER 9 TIMEBASE TIMER       209         9.1 Overview of the Timebase Timer       210         9.2 Configuration of the Timebase Timer       212         9.3 Timebase Timer Control Register (TBTC)       214         9.4 Timebase Timer Interrupts       216         9.5 Operation of the Timebase Timer       217         9.6 Usage Notes on the Timebase Timer       220         9.7 Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1 Overview of the Watchdog Timer       224         10.2 Configuration of the Watchdog Timer       225         10.3 Watchdog Timer Control Register (WDTC)       227         10.4 Operation of the Watchdog Timer       229         10.5 Usage Notes on the Watchdog Timer       231         10.6 Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1 Overview of the 16-Bit Reload Timer       234         11.2 Configuration of the 16-Bit Reload Timer       237         11.3 16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 8.9   | .2 Operation of Port 6                        | 205 |

| 9.1       Overview of the Timebase Timer       210         9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer Program       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       229         10.5       Usage Notes on the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1       Overview of the 16-Bit Reload Timer       234         11.2       Configuration of the 16-Bit Reload Timer       237         11.3       16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 8.10  | Sample I/O Port Program                       | 207 |

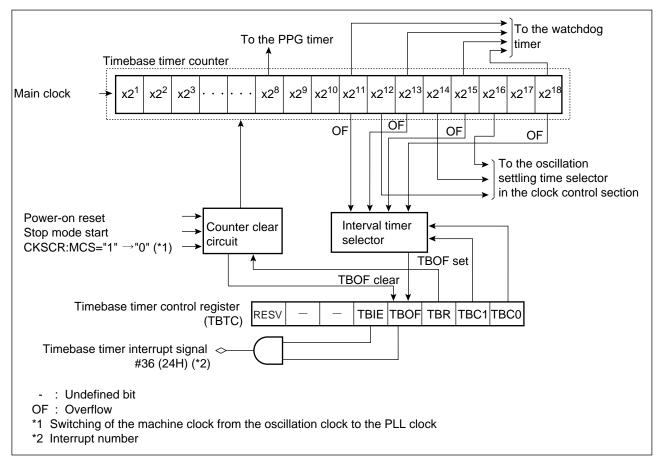

| 9.2       Configuration of the Timebase Timer       212         9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       229         10.5       Usage Notes on the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1       Overview of the 16-Bit Reload Timer       234         11.2       Configuration of the 16-Bit Reload Timer       237         11.3       16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | CHAP  | TER 9 TIMEBASE TIMER                          | 209 |

| 9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10       WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       229         10.5       Usage Notes on the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         CHAPTER 11       16-BIT RELOAD TIMER       233         11.1       Overview of the 16-Bit Reload Timer       234         11.2       Configuration of the 16-Bit Reload Timer       237         11.3       16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9.1   | Overview of the Timebase Timer                | 210 |

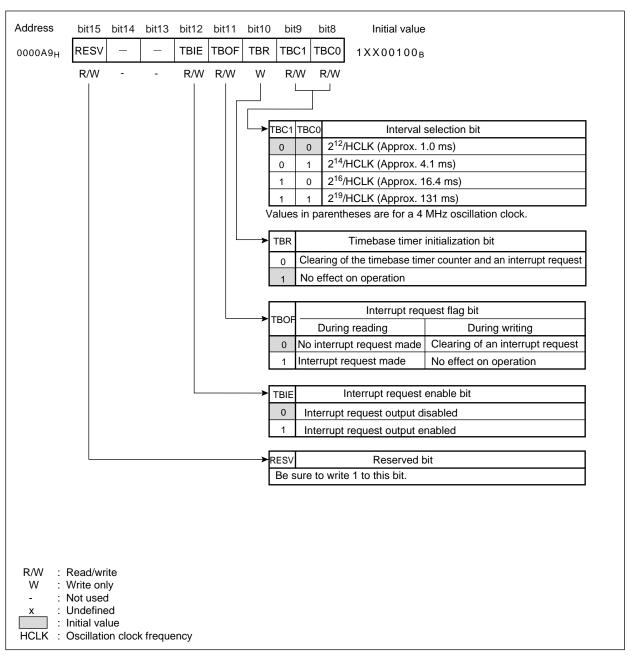

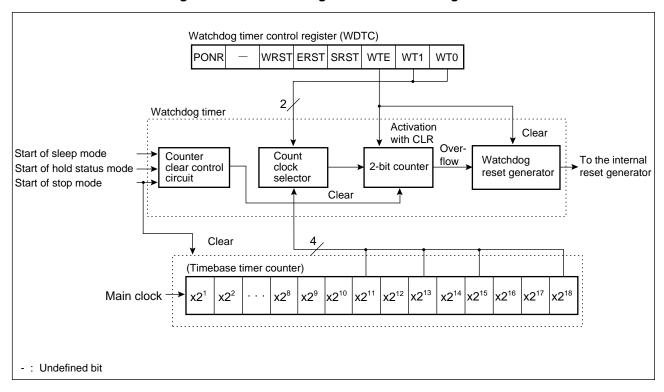

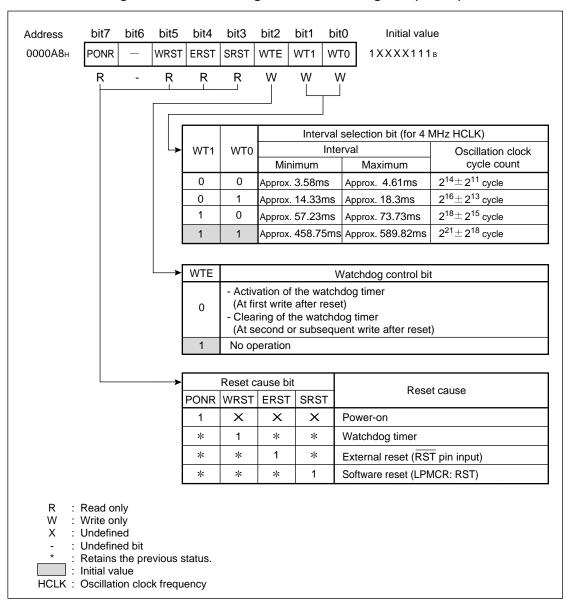

| 9.3       Timebase Timer Control Register (TBTC)       214         9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10       WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       229         10.5       Usage Notes on the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         CHAPTER 11       16-BIT RELOAD TIMER       233         11.1       Overview of the 16-Bit Reload Timer       234         11.2       Configuration of the 16-Bit Reload Timer       237         11.3       16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 9.2   | Configuration of the Timebase Timer           | 212 |

| 9.4       Timebase Timer Interrupts       216         9.5       Operation of the Timebase Timer       217         9.6       Usage Notes on the Timebase Timer       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       229         10.5       Usage Notes on the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1       Overview of the 16-Bit Reload Timer       234         11.2       Configuration of the 16-Bit Reload Timer       237         11.3       16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 9.3   | <del>-</del>                                  |     |

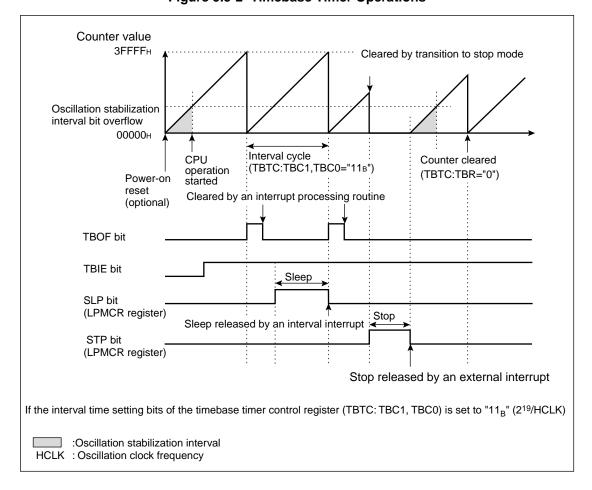

| 9.6       Usage Notes on the Timebase Timer       220         9.7       Sample Program for the Timebase Timer Program       221         CHAPTER 10 WATCHDOG TIMER       223         10.1       Overview of the Watchdog Timer       224         10.2       Configuration of the Watchdog Timer       225         10.3       Watchdog Timer Control Register (WDTC)       227         10.4       Operation of the Watchdog Timer       229         10.5       Usage Notes on the Watchdog Timer       231         10.6       Sample Program for the Watchdog Timer       232         CHAPTER 11 16-BIT RELOAD TIMER       233         11.1       Overview of the 16-Bit Reload Timer       234         11.2       Configuration of the 16-Bit Reload Timer       237         11.3       16-Bit Reload Timer Pins       239                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 9.4   | ÷ , , ,                                       |     |